4.902,19 TL + KDV

Stok Durumu:

Yok

Not

:

Kampanya

{{CMP.TITLE}}

{{CMP.DESCRIPTION}}

- Ürün Özellikleri

- İade ve Teslimat

- Ödeme Seçenekleri

- Yorumlar (0)

- Beni Ara

- Ek

-

FPGA Core Board, Features The XILINX Spartan-3E Chip XC3S500E Onboard

Overview

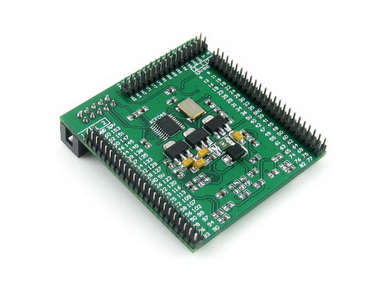

Core3S500E is an FPGA core board that features an XC3S500E device onboard, supports further expansion.

- onboard 1pcs XCF04S

- integrated FPGA basic circuit, such as clock circuit

- onboard nCONFIG button, RESET button, 4 x LEDs

- all the I/O ports are accessible on the pin headers

- onboard JTAG debugging/programming interface

- 2.0mm header pitch design, suitable for being plugged-in your application system

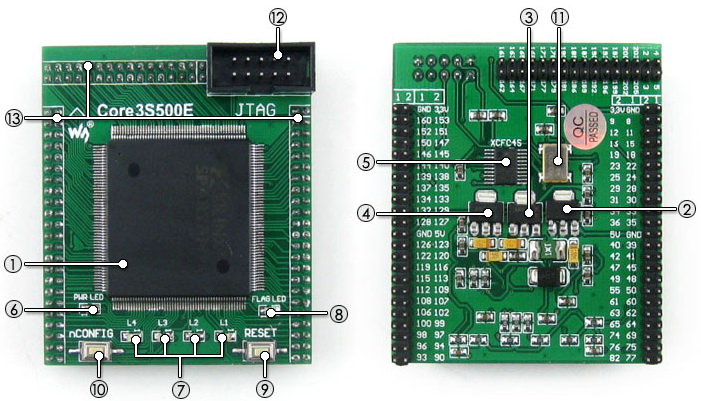

What's On Board

- XC3S500E:the XILINX Spartan-3E FPGA device which features:

- Operating Frequency: 50MHz

- Operating Voltage: 1.15V~3.3V

- Package: QFP208

- I/Os: 116

- LEs: 500K

- RAM: 360kb

- DCMs: 4

- Debugging/Programming: supports JTAG

- AMS1117-3.3, 3.3V voltage regulator

- AMS1117-2.5, 2.5V voltage regulator

- AMS1117-1.2, 1.2V voltage regulator

- XCF04S, onboard serial FLASH memory, for storing code

- Power indicator

- LEDs

- FPGA initialization indicator

- Reset button

- nCONFIG button: for re-configuring the FPGA chip, the equivalent of power reseting

- 50M active crystal oscillator

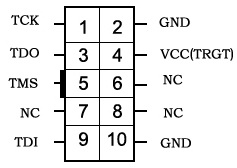

- JTAG interface: for debugging/programming

- FPGA pins expander, VCC, GND and all the I/O ports are accessible on expansion connectors for further expansion

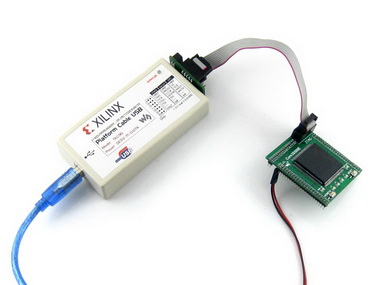

Photos

Note:

Core3S500E provides JTAG debugging interface, yet does NOT integrate any debugging function, a debugger is required.

Mother board and programmer/debugger in the photos are NOT included in the price.

Debugging/Programming Interface

The Core3S500E FPGA core board integrates JTAG interface for programming/debugging.

Package Contains

- Core3S500E core board x 1

Development Resources

- Related software (Xilinx ISE 12 - supports Winxp/Win7, doesn't support Win8)

- Demo code (Verilog, VHDL)

- Schematic (PDF)

- FPGA development documentations

Wiki: www.waveshare.com/wiki/Core3S500E